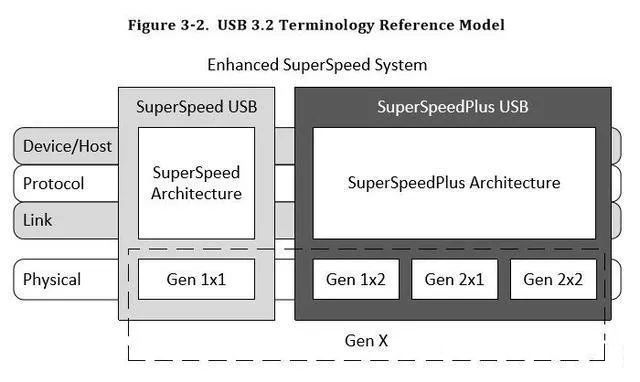

USB-IF Mae'r confensiwn enwi USB diweddaraf yn nodi na fydd y USB3.0 a'r USB3.1 gwreiddiol yn cael eu defnyddio mwyach, gelwir yr holl safonau USB3.0 yn USB3.2, a bydd safonau USB3.2 yn ymgorffori'r hen ryngwyneb USB 3.0/3.1 i gyd i mewn i'r safon USB3.2, gelwir rhyngwyneb USB3.1 USB3.2 Gen 2, a gelwir y rhyngwyneb USB3.0 gwreiddiol yn USB3.2 Gen 1, gan ystyried cydnawsedd, trosglwyddiad USB3.2 Gen 1 cyflymder yw 5Gbps, cyflymder trosglwyddo USB3.2 Gen2 yw 10Gbps, cyflymder trosglwyddo USB3.2 Gen2x2 yw 20Gbps, felly gellir deall diffiniadau manyleb newydd USB3.1 Gen1 a USB3.0 fel un peth, ond mae'r enw yn wahanol. Deellir bod Gen1 a Gen2 yn golygu bod y dull amgodio yn wahanol, mae'r defnydd lled band yn wahanol, ac mae Gen1 a Gen1x2 yn sianeli gwahanol yn reddfol. Ar hyn o bryd, mae'n hysbys bod gan lawer o famfyrddau pen uchel ryngwyneb USB3.2Gen2x2, mae rhai yn rhyngwyneb MATH C, mae rhai yn rhyngwyneb USB, ac mae'r rhyngwyneb MATH C presennol yn bennaf. Y gwahaniaeth rhwng Gen1 a Gen2, Gen3

Cymhariaeth o USB3.2 a'r USB4 diweddaraf

1. Lled band trosglwyddo: Mae USB 3.2 hyd at 20Gbps, tra bod USB4 yn 40Gbps.

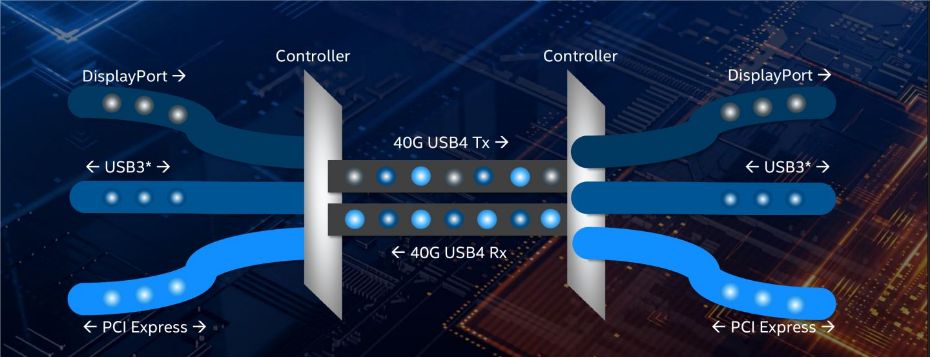

2. Protocol trosglwyddo: Mae USB 3.2 yn bennaf yn trosglwyddo data trwy'r protocol USB, neu'n ffurfweddu USB a DP trwy DP Alt Mode (modd amgen). Mae USB4 yn amgáu protocolau USB 3.2, DP a PCIe i mewn i becynnau trwy dechnoleg twnelu ac yn eu hanfon ar yr un pryd.

3. DP trawsyrru: gall gefnogi DP 1.4. Mae USB 3.2 yn ffurfweddu'r allbwn trwy DP Alt Mode; Yn ogystal â ffurfweddu'r allbwn trwy DP Alt Mode (modd amgen), gall USB4 hefyd dynnu data DP trwy becynnau protocol twnelu USB4.

4, trosglwyddiad PCIe: nid yw USB 3.2 yn cefnogi PCIe, mae USB4 yn cefnogi. Mae data PCIe yn cael ei dynnu trwy becynnau protocol twnelu USB4.

5, trosglwyddiad TBT3: ni chefnogir USB 3.2, cefnogir USB4, hynny yw, trwy becynnau protocol twnnel USB4 i dynnu data PCIe a DP.

6, Host to Host: cyfathrebu rhwng gwesteiwr a gwesteiwr, nid yw USB3.2 yn cefnogi, cefnogaeth USB4. Yn bennaf mae USB4 yn cefnogi'r protocol PCIe i gefnogi'r swyddogaeth hon.

Nodyn: Gellir ystyried twnelu fel techneg ar gyfer cyfuno data o wahanol brotocolau, gan ddefnyddio penawdau i wahaniaethu rhwng mathau.

Yn USB 3.2, mae trosglwyddiad fideo DisplayPort a data USB 3.2 yn cael ei drosglwyddo ar wahanol addaswyr sianel, tra yn USB4, gellir trosglwyddo fideo DisplayPort, data USB 3.2 a data PCIe ar yr un sianel, sef y gwahaniaeth mwyaf rhwng y ddau. Gallwch weld y ffigur isod i ddyfnhau eich dealltwriaeth.

Gellir dychmygu sianeli USB4 fel lonydd a all basio gwahanol fathau o gerbydau, a gellir dychmygu data USB, data DP, a data PCIe fel cerbydau gwahanol. Mae yna wahanol geir yn yr un lôn yn gyrru'n drefnus, ac mae USB4 yn trosglwyddo gwahanol fathau o ddata ar yr un sianel. Mae data USB3.2, DP a PCIe yn cael eu cydgrynhoi gyda'i gilydd yn gyntaf, eu hanfon trwy'r un sianel, eu hanfon at ddyfeisiau ei gilydd, ac yna eu gwahanu'n 3 math gwahanol o ddata.

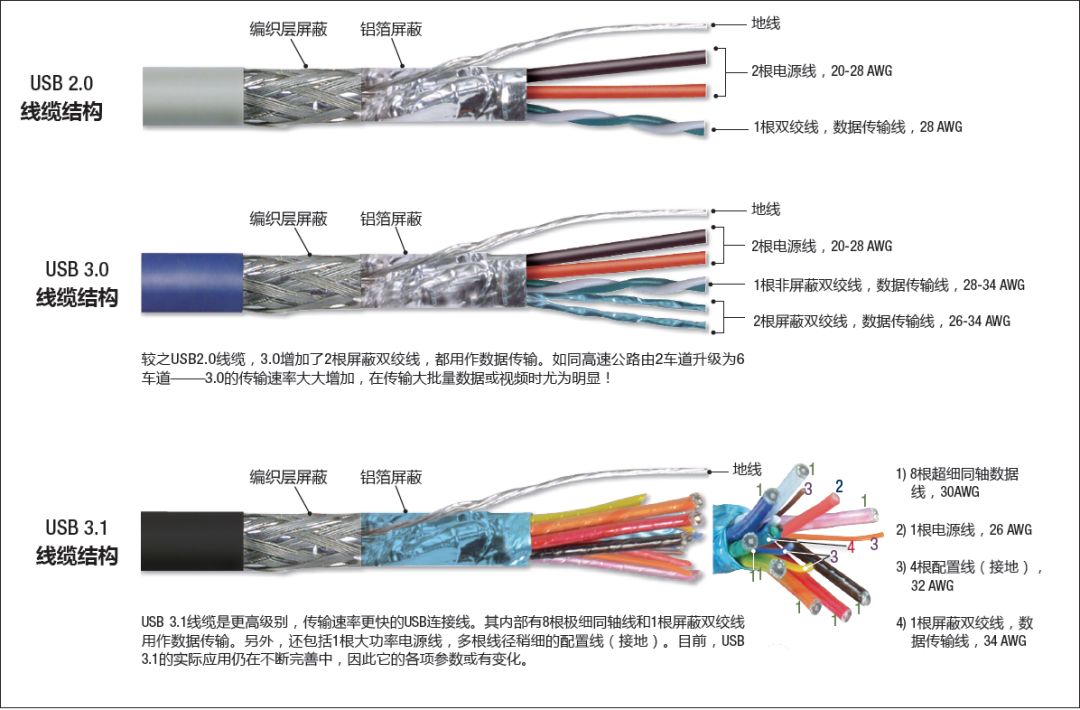

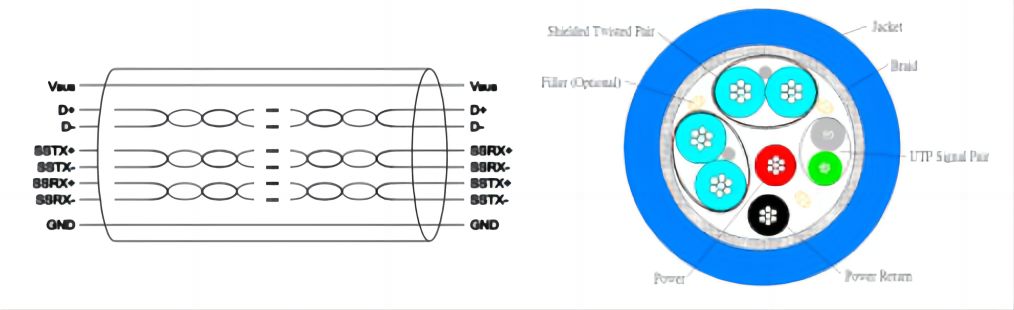

Diffiniad strwythur cebl USB3.2

Yn y fanyleb USB 3.2, mae natur cyflymder uchel USB Math-C yn cael ei ddefnyddio'n llawn. Mae gan USB Type-C 2 sianel trosglwyddo data cyflym, a enwyd (TX1 +/TX1-, RX1 +/RX1-) a (TX2 +/TX2-, RX2 +/RX2-), yn flaenorol dim ond un o'r sianeli a ddefnyddiodd USB 3.1 i drosglwyddo data , ac roedd y sianel arall yn bodoli mewn ffordd wrth gefn. Yn USB 3.2, gellir galluogi'r ddwy sianel pan fo'n briodol, a gellir cyflawni'r cyflymder trosglwyddo uchaf o 10Gbps y sianel, fel bod y swm yn 20Gbps, gan ddefnyddio amgodio 128b / 132b, gall y cyflymder data gwirioneddol gyrraedd tua 2500MB / s, sy'n yn union ddwbl y USB 3.1 heddiw. Mae'n werth nodi bod newid sianel USB 3.2 yn gwbl ddi-dor ac nid oes angen gweithrediad arbennig gan y defnyddiwr.

Mae ceblau USB3.1 yn cael eu trin yn yr un modd â USB 3.0. Rheoli rhwystriant: Rheolir rhwystriant llinell wahaniaethol cysgodol y CDP ar 90Ω ±5Ω, a rheolir y llinell gyfechelog un pen ar 45Ω ±3Ω. Mae'r oedi y tu mewn i'r pâr gwahaniaethol yn llai na 15ps / m, ac mae gweddill y golled mewnosod a dangosyddion eraill yn gyson â USB3.0, a dewisir strwythur y cebl yn unol â swyddogaethau a chategorïau senarios a gofynion y cais: VBUS: 4 gwifrau i sicrhau cerrynt y foltedd a'r cerrynt; Vconn: yn wahanol i VBUS, dim ond ystod foltedd o 3.0 ~ 5.5V y mae'n ei ddarparu; Dim ond pweru sglodion y cebl; D +/D-: signal USB 2.0, er mwyn cefnogi plygio ymlaen a gwrthdroi, mae dau bâr o signalau ar ochr y soced; TX+/- a RX+/-: 2 set o signalau, 4 pâr o signalau, cefnogi rhyngosod ymlaen a gwrthdroi; CC: Ffurfweddu signalau, cadarnhau a rheoli cysylltiadau ffynhonnell-derfynell; SUB: Signal swyddogaeth estynedig, ar gael ar gyfer sain.

Os yw rhwystriant y llinell wahaniaethol gysgodol yn cael ei reoli ar 90Ω ±5Ω, defnyddir y llinell gyfechelog, mae dychweliad daear y signal trwy'r GND wedi'i gysgodi, a rheolir y llinell gyfechelog un pen ar 45Ω±3Ω, ond o dan wahanol hyd ceblau. , mae senarios cais y rhyngwyneb yn pennu dewis cysylltiadau a dewis strwythur cebl.

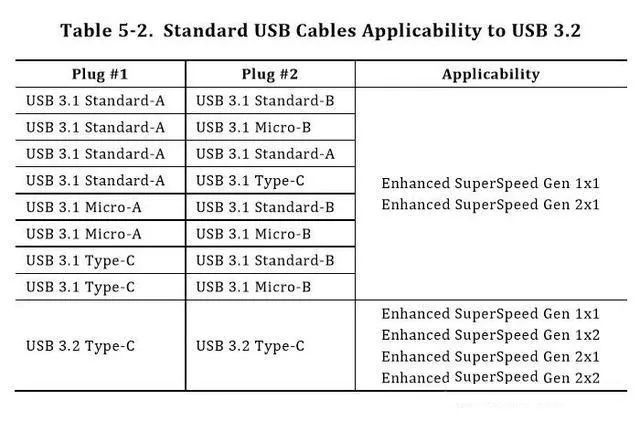

USB 3.2 Gen 1x1 - SuperSpeed, 5 Gbit/s (0.625 GB/s) cyfradd signalau data dros 1 lôn gan ddefnyddio amgodio 8b/10b, yr un fath â USB 3.1 Gen 1 a USB 3.0.

USB 3.2 Gen 1x2 - SuperSpeed+, cyfradd data 10 Gbit/s (1.25 GB/s) newydd dros 2 lôn gan ddefnyddio amgodio 8b/10b.

USB 3.2 Gen 2x1 - Cyfradd data SuperSpeed+, 10 Gbit/s (1.25 GB/s) dros 1 lôn gan ddefnyddio amgodio 128b/132b, yr un peth â USB 3.1 Gen 2.

USB 3.2 Gen 2x2 - SuperSpeed+, cyfradd data 20 Gbit/s (2.5 GB/s) newydd dros 2 lôn gan ddefnyddio amgodio 128b/132b.

E-bost:francesgu1225@hotmail.com

E-bost:francesgu1225@gmail.com

WhatsAPP:+8618689452274

Amser post: Gorff-18-2023